Para generación de código eficiente desde modelos de Máquina de Estado hacia Lenguajes de Descripción de Hardware (HDL) tal como VHDL, Verilog y SystemC, aplique estas prácticas de diseño.

En un modelo de Máquina de Estado HDL, los siguientes son esperados:

|

Designar Disparadores de Conducción |

|

Establecer Mapeo de Disparador-Puerto |

|

Lógica de Estado Activo |

Como

Tema |

Detalle |

Ver También |

||||||||||||||||||||||||||||||||

Designar Disparadores de Conducción |

|

|||||||||||||||||||||||||||||||||

Establecer Mapeo de Disparador-Puerto |

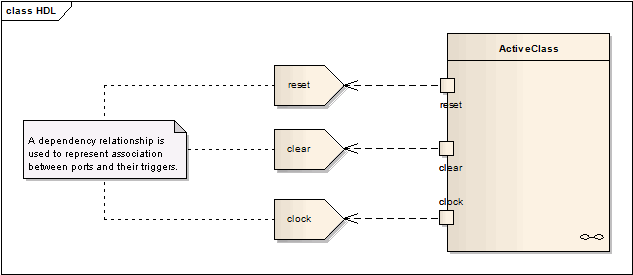

Después de modelar exitosamente los diferentes modos de operación del componente, y los disparadores asociados con ellos, debe asociar los disparadores con los puertos del componente Una relación de Dependencia desde el Puerto hacia el disparador asociado es utilizado para significar su asociación

|

|

||||||||||||||||||||||||||||||||

Lógica de Estado Activo |

Los primeros dos aspectos, arriba, ponen en marcha los preliminares necesarios para la interpretación eficiente de los componentes de hardware. La lógica de Máquina de Estado real es ahora modelada dentro del estado Activo (Submáquina).

|

|

||||||||||||||||||||||||||||||||

Notas

|

Para ser capaz de generar código desde modelos conductuales, todas las construcciones conductuales deberían estar contenidas dentro de una Clase |

|

El motor de generación de código actual soporta sólo un disparador de reloj para un componente |

Aprender más