Para la generación de código eficiente de los modelos de máquina de estado a los lenguajes de descripción de hardware, Hardware Description Languages (HDL), como por ejemplo VHDL, Verilog y SystemC, aplican las practicas de diseño descritas en este tema.

En un modelo de la máquina de estado HDL, se espera lo siguiente:

| • | Designar disparadores de transmisión |

| • | Establecer trazado del puerto del disparador |

| • | Lógica de estado activa |

Designar disparadores de transmisión

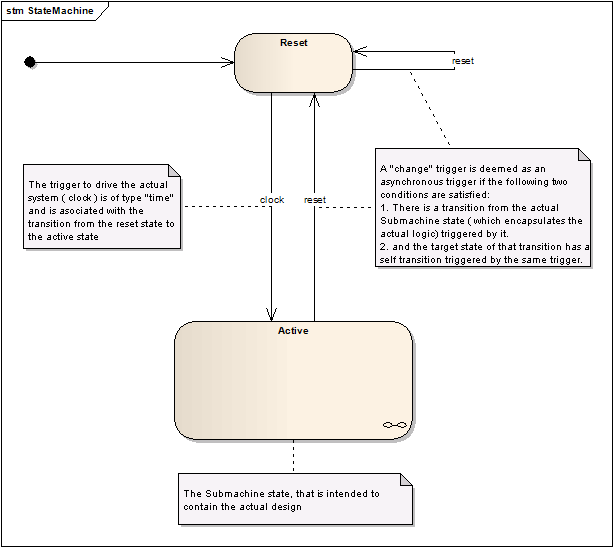

El diagrama de máquina de estado de alto nivel debería usarse para modelar los modos diferentes de un componente de hardware, y los disparadores asociados que los dirigen, como se muestra en el siguiente diagrama.

Disparadores asíncronos

Los disparadores asíncronos deberían modelarse de acuerdo al siguiente patrón:

| 1. | El disparador debería ser del tipo Change (especificación: true / false) |

| 2. | El estado activo (Estado de sub máquina) debería tener un disparador de transición. |

| 3. | El estado de destino de la transición con el disparador debería tener una auto transición con el mismo disparador. |

Reloj

Un disparador del tipo Time, que dispara las transiciones al estado activo (Estado de sub máquina) es considerado como el Reloj. La especificación de este disparador debería ser específica al lenguaje de destino.

Especificaciones del disparador reloj

Tipo de disparador |

Lenguaje |

Especificación |

|

Borde positivo disparado |

Borde negativo disparado |

||

Time |

VHDL |

rising_edge |

falling_edge |

Verilog |

posedge |

negedge |

|

SystemC |

positive |

negative |

|

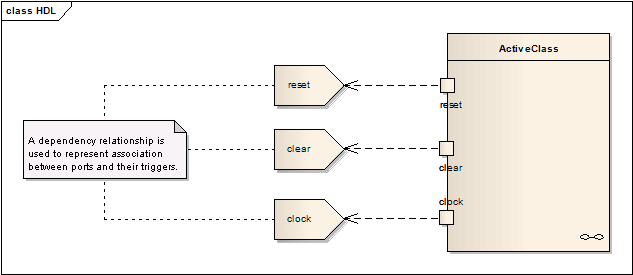

Establecer el puerto – Trazado del disparador

Luego de modelar exitosamente los diferentes modos operativos del componente, y los disparadores asociados a estos, debe asociar los disparadores con los puertos del componente como se muestra en el siguiente diagrama.

Una relación de dependencia desde el puerto al disparador asociado se debería usar mostrar esta asociación.

Vea también:

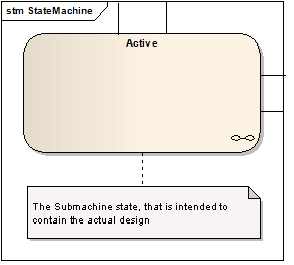

Lógica del estado activo

Los dos primeros aspectos, arriba, colocan las preliminarias requeridas para una interpretación eficiente de los componentes de hardware. La lógica de la máquina de estado actual ahora se modela dentro del estado Activo (Sub máquina).

Tenga en cuenta: |

La máquina de generación de código actual soporta sólo un disparador reloj para un componente. |